前言

VT圖(threshold voltage distribution)為分析 Flash很重要的參考圖,但要了解其圖形的由來有很多原理需要了解,這篇文章為介紹Nand Flash VT圖的第一篇,從基本原理開始,說明read level與Vth的關係。

1. MOSFET、Vth

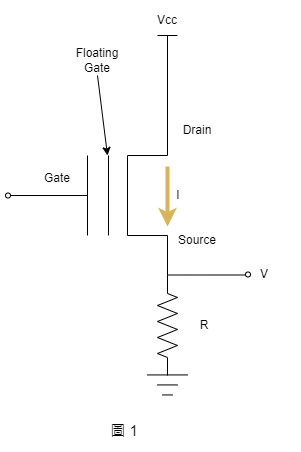

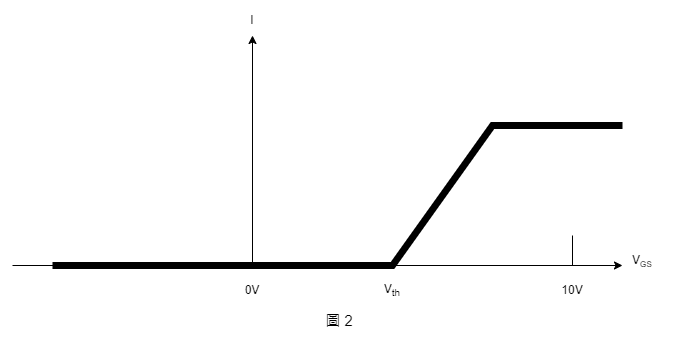

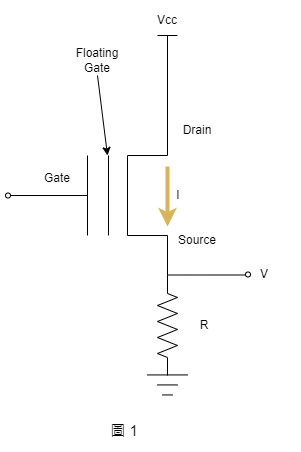

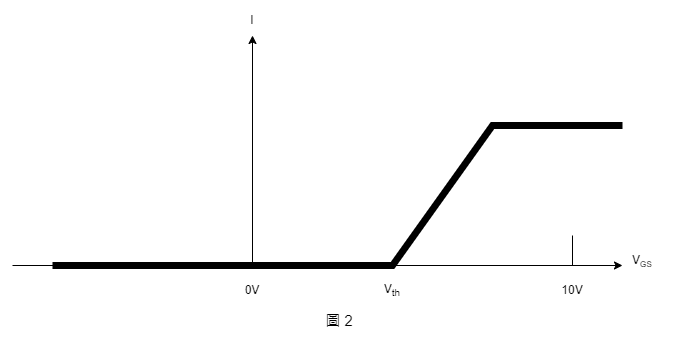

- 上圖1為Nand Flash最基本的儲存單元,稱為一個cell,每個cell都是一個FGMOS(Floating-gate MOSFET)組成,也就是多了一層Floating Gate的MOSFET,MOFET可想成一個可以控制的電阻,在Gate跟Source之間加一個電壓Vgs,會改變 Drain跟Source之間的電流I,間接改變電壓V,也就是我們要量的電壓,其I-V曲線可以畫成下圖2:

- 可以看到Vgs小於Vth時,電流I都是0,Cell不導通,因此這時的量到的電壓V=0。當Vgs大於Vth,Cell導通,電流I開始慢慢增加,電壓V則會變大。這個Vth稱為導通電壓,Vth越大,cell越不容易導通。

2. Floating Gate、Read電壓

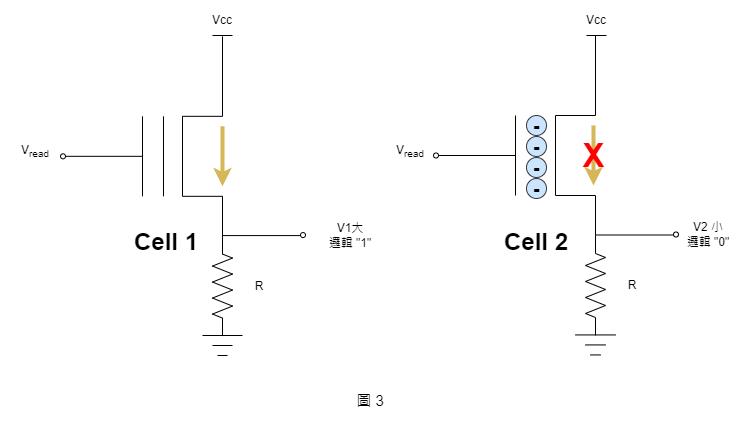

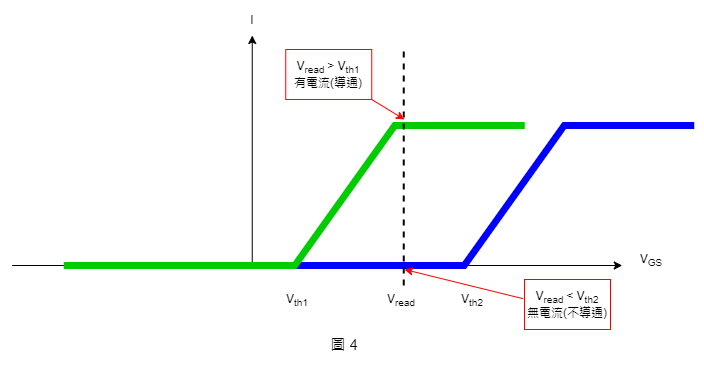

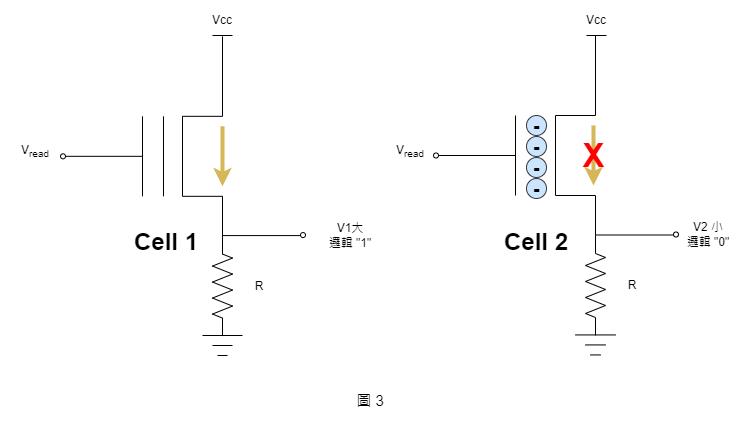

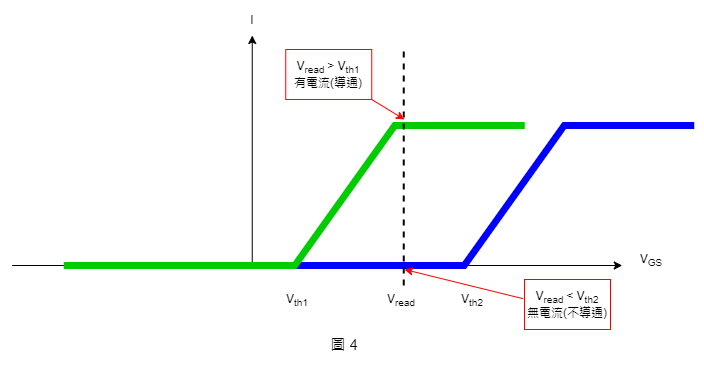

- 而Floating Gate的功能則是可以儲存電子,改變Vth的大小。儲存的原理是利用量子力學的穿隧效應(tunneling effect),要注意的是穿隧效應發生是機率性的,這個特性會影響後面VT圖的長相。當Floating Gate中存在電子時,等於在Gate跟Source之間內建了一個負的偏壓,Vth變大,因此若有兩個cell,Cell 1沒有存電子,Cell 2有,對它們加上同樣的Vread,Cell 1會導通,Cell 2 不會導通,讀出的電壓V1、V2就會不同,參考圖3跟圖4。

- Floating Gate沒有電子的狀態稱為Erase,讀出來的電壓為邏輯"1",強調邏輯兩個字是因為讀出的電壓是高或低要看電路如何設計,並不一定如圖中有電子V就小,而不同電壓代表的定義也是可以改的,所以不用太糾結電壓大小,知道是不同狀態即可。

3. Erase、Program

- 正的高壓可以讓電子存進cell中,稱為Vprog,而負的高壓可以把電子趕出cell,稱為Verase,program、erase跟read的操作電壓不相同,概略值為Erase -20V,program +20V,read 0~10V。

4. SLC、MLC、Read Level

-

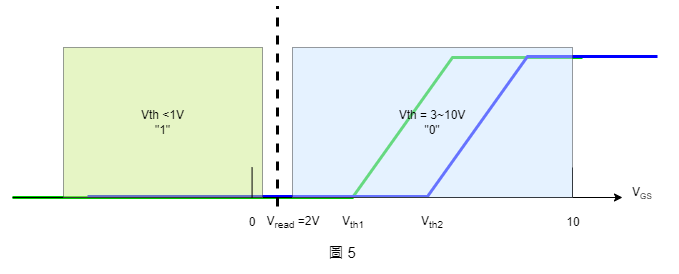

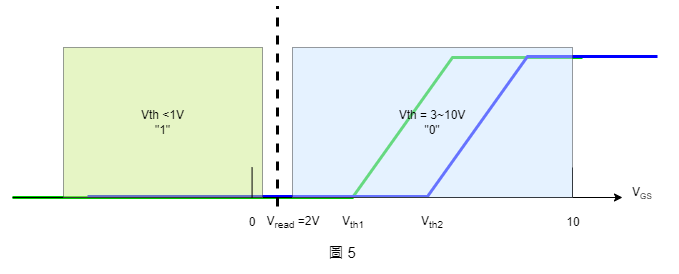

前面所談的都是Floating Gate有電子跟沒有電子,也就是一個Cell只有"0"跟"1"的狀態,這樣的使用方式稱為SLC (single-level cell),如圖5,我們只需要一個Vread即可分辨cell的狀態,而Vth可以容許的誤差範圍很大。

-

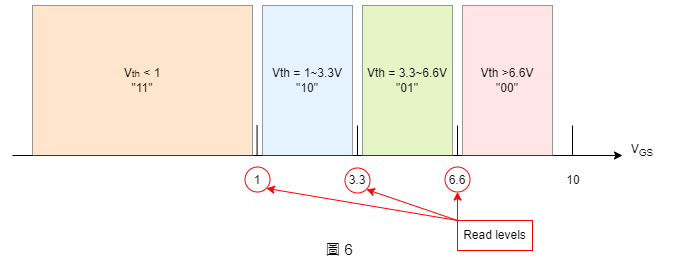

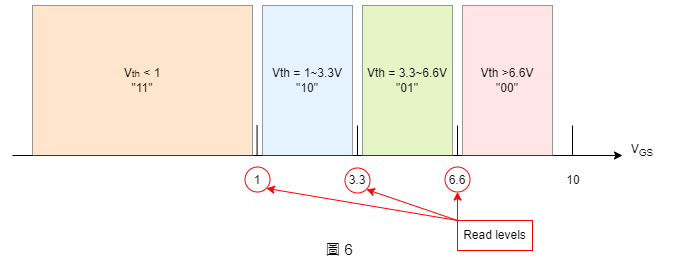

隨著技術進步,我們可以對Vth控制得更精準之後,就出現了MLC (multi-level cell)的使用方式,使同樣一個cell變成可以儲存2個位元(bit)的資料,參考圖6,我們只要依序加上1V、3.3V、6.6V,紀錄各個cell在何時導通,就可以分辨出該cell儲存的資訊為何。而不同的Vread就稱為Read Level。

-

目前的Nand Flash大多使用的是TLC、QLC的操作方式,也就是一個cell儲存3bit、4bit,其原理與MLC相同,只是將Vth切得更細、Read Level也分更多階。

小結

以我自己的經驗Vth 跟Read Level很容易搞混,簡而言之,Vth大小代表Cell中儲存的電荷量,而讀取電壓Vread則是分辨Cell狀態時所施加的偏壓,帶著這兩個概念,我們就可以進入到下一篇,學習如何把VT圖畫出來。

[Nand Flash] 看懂VT圖 - 2 繪製VT圖